Here is how I got my Hynix A-Die DDR5 stable at 6400MHz with the below timings. It should be the same method for Hynix M-Die as well.

![Font Technology Screenshot Software Electric blue]()

First, load a memory profile for say 6200 from your motherboard. Set the RAM speed to 6400.

Next set your BUS settings to the @Veii recommended.

![Font Screenshot Technology Slope Software]()

Here are the voltages I use for 6400MHz.

![Font Slope Screenshot Technology Software]()

Next, set your timings rather high, like the below., the columns on the right. Then reboot.

![Font Screenshot Software Slope Parallel]()

![Font Screenshot Software Technology Slope]()

Hynix DDR5 doesn't mind really low tRFC. Set the tRFC mini like below to start, then raise the tRC number until your PC boots, or lower it until your PC doesn't boot. Then when your PC doesn't boot, raise the tRC number one higher.

docs.google.com

docs.google.com

![Rectangle Font Line Screenshot Parallel]()

Once it's as low you can go, you're good, though you might need to raise it one notch higher than the lowest it'll boot.

Now run Karhu RAM test for minimum of five minutes, max ten minutes. I find if it doesn't find an error within 5 minutes I'm normally fine.

Now lower just your tRCDRD and tRP to 39 or 38.

Ran Karhu again. Lower tRCDRD and tRP one notch at a time until Karhu gets errors, then raise it one notch and let it run with no errors.

I find that doing tRCDRD and tRP first are the most important to get stable.

Next lower tCL and tRAS until you get errors in Karhu. Then raise them both back one notch higher so that you get no errors.

Next, do the same with tWR.

Then try tRTP at 20, it should be fine, if not try a notch higher.

Set tFAW to 16 and raise it one notch at a time until you get no errors. Between 16-20 should be good.

Next, set the TRRDs TtWTRs to 3-15 or 4-16. Test again.

Set ScLs to 4-4 or 4-2. Test again.

Set TrdrdSc and Sd to 5-5 and TwrwrSd and Dd to 7-7. The rest of those timings as you see below in the left timings column. Test again.

Also, if your BIOS support adjusting Refresh Interval/tREFI, set it at max, and test, if it passes, good, if not, reduce it by say 1024, and then test again.

Repeat until you get no errors in Karhu Ram Test and finally, TM5.

You can see the MB/sec by hovering your cursor over the Coverage % in Karhu.

![Font Screenshot Software Technology Slope]()

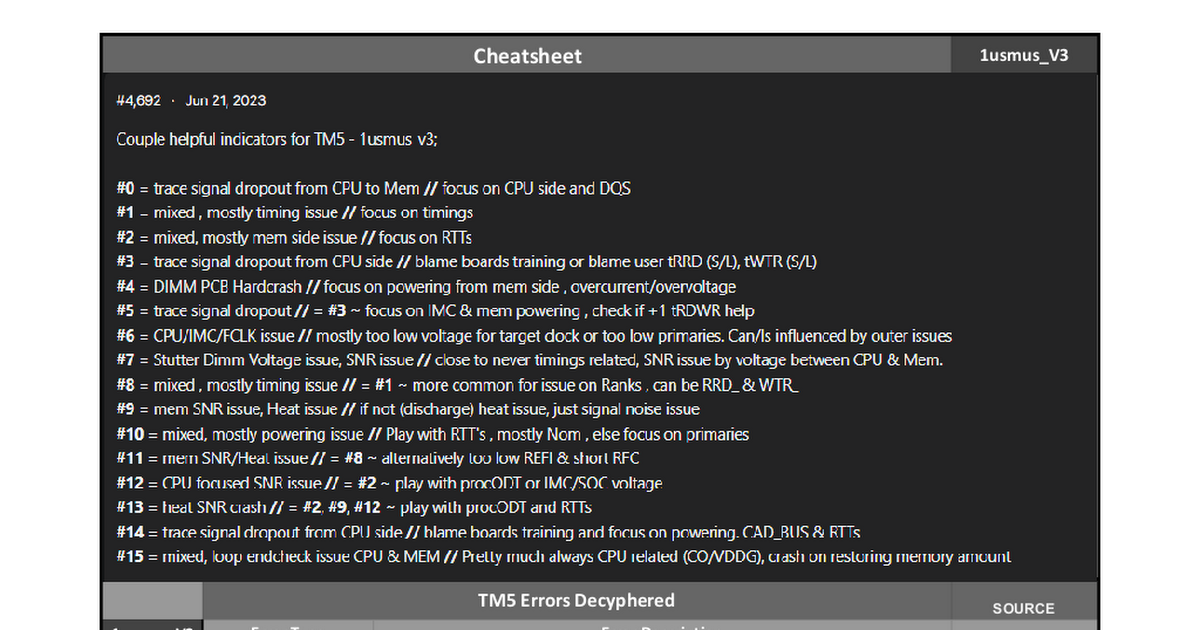

Next, run TM5 1usmus_v3 for 25 cycles. You should be able to find your stable settings easily by using this method within a few hours of tweaking the timings before running TM5.

First, load a memory profile for say 6200 from your motherboard. Set the RAM speed to 6400.

Next set your BUS settings to the @Veii recommended.

Here are the voltages I use for 6400MHz.

Next, set your timings rather high, like the below., the columns on the right. Then reboot.

Hynix DDR5 doesn't mind really low tRFC. Set the tRFC mini like below to start, then raise the tRC number until your PC boots, or lower it until your PC doesn't boot. Then when your PC doesn't boot, raise the tRC number one higher.

DDR4/5 Helper by Veii

Once it's as low you can go, you're good, though you might need to raise it one notch higher than the lowest it'll boot.

Now run Karhu RAM test for minimum of five minutes, max ten minutes. I find if it doesn't find an error within 5 minutes I'm normally fine.

Now lower just your tRCDRD and tRP to 39 or 38.

Ran Karhu again. Lower tRCDRD and tRP one notch at a time until Karhu gets errors, then raise it one notch and let it run with no errors.

I find that doing tRCDRD and tRP first are the most important to get stable.

Next lower tCL and tRAS until you get errors in Karhu. Then raise them both back one notch higher so that you get no errors.

Next, do the same with tWR.

Then try tRTP at 20, it should be fine, if not try a notch higher.

Set tFAW to 16 and raise it one notch at a time until you get no errors. Between 16-20 should be good.

Next, set the TRRDs TtWTRs to 3-15 or 4-16. Test again.

Set ScLs to 4-4 or 4-2. Test again.

Set TrdrdSc and Sd to 5-5 and TwrwrSd and Dd to 7-7. The rest of those timings as you see below in the left timings column. Test again.

Also, if your BIOS support adjusting Refresh Interval/tREFI, set it at max, and test, if it passes, good, if not, reduce it by say 1024, and then test again.

Repeat until you get no errors in Karhu Ram Test and finally, TM5.

You can see the MB/sec by hovering your cursor over the Coverage % in Karhu.

Next, run TM5 1usmus_v3 for 25 cycles. You should be able to find your stable settings easily by using this method within a few hours of tweaking the timings before running TM5.