Voici comment j'ai rendu ma Hynix A-Die DDR5 stable à 6400 MHz avec les timings ci-dessous. Cela devrait être la même méthode pour Hynix M-Die.

![Font Technology Screenshot Software Electric blue]()

Tout d'abord, chargez un profil de mémoire pour, disons, 6200 à partir de votre carte mère. Réglez la vitesse de la RAM sur 6400.

Ensuite, définissez vos paramètres BUS sur ceux recommandés par @Veii.

![Font Screenshot Technology Slope Software]()

Voici les tensions que j'utilise pour 6400 MHz.

![Font Slope Screenshot Technology Software]()

Ensuite, définissez vos timings assez élevés, comme ci-dessous, les colonnes de droite. Puis redémarrez.

![Font Screenshot Software Slope Parallel]()

![Font Screenshot Software Technology Slope]()

Hynix DDR5 ne se soucie pas vraiment des tRFC très bas. Définissez le tRFC mini comme ci-dessous pour commencer, puis augmentez le nombre tRC jusqu'à ce que votre PC démarre, ou diminuez-le jusqu'à ce que votre PC ne démarre pas. Ensuite, lorsque votre PC ne démarre pas, augmentez le nombre tRC d'un.

docs.google.com

docs.google.com

![Rectangle Font Line Screenshot Parallel]()

Une fois que c'est aussi bas que vous pouvez aller, vous êtes bon, bien que vous puissiez avoir besoin de l'augmenter d'un cran de plus que le plus bas qu'il démarrera.

Maintenant, exécutez le test Karhu RAM pendant au moins cinq minutes, au maximum dix minutes. Je constate que si cela ne trouve pas d'erreur dans les 5 minutes, je vais normalement bien.

Maintenant, baissez simplement votre tRCDRD et tRP à 39 ou 38.

Karhu a de nouveau couru. Baissez tRCDRD et tRP d'un cran à la fois jusqu'à ce que Karhu obtienne des erreurs, puis augmentez-le d'un cran et laissez-le fonctionner sans erreurs.

Je constate que faire tRCDRD et tRP en premier est le plus important pour devenir stable.

Ensuite, baissez tCL et tRAS jusqu'à ce que vous obteniez des erreurs dans Karhu. Ensuite, augmentez-les tous les deux d'un cran, de sorte que vous n'obteniez aucune erreur.

Ensuite, faites de même avec tWR.

Ensuite, essayez tRTP à 20, cela devrait aller, sinon, essayez un cran plus haut.

Définissez tFAW sur 16 et augmentez-le d'un cran à la fois jusqu'à ce que vous n'obteniez aucune erreur. Entre 16 et 20 devrait être bon.

Ensuite, définissez les TRRDs TtWTRs sur 3-15 ou 4-16. Testez à nouveau.

Définissez ScLs sur 4-4 ou 4-2. Testez à nouveau.

Définissez TrdrdSc et Sd sur 5-5 et TwrwrSd et Dd sur 7-7. Le reste de ces timings comme vous le voyez ci-dessous dans la colonne de gauche des timings. Testez à nouveau.

De plus, si votre BIOS prend en charge le réglage de l'intervalle de rafraîchissement/tREFI, définissez-le au maximum et testez, si cela réussit, bien, sinon, réduisez-le de, disons, 1024, puis testez à nouveau.

Répétez jusqu'à ce que vous n'obteniez aucune erreur dans Karhu Ram Test et enfin TM5.

Vous pouvez voir le Mo/s en survolant le % de couverture dans Karhu.

![Font Screenshot Software Technology Slope]()

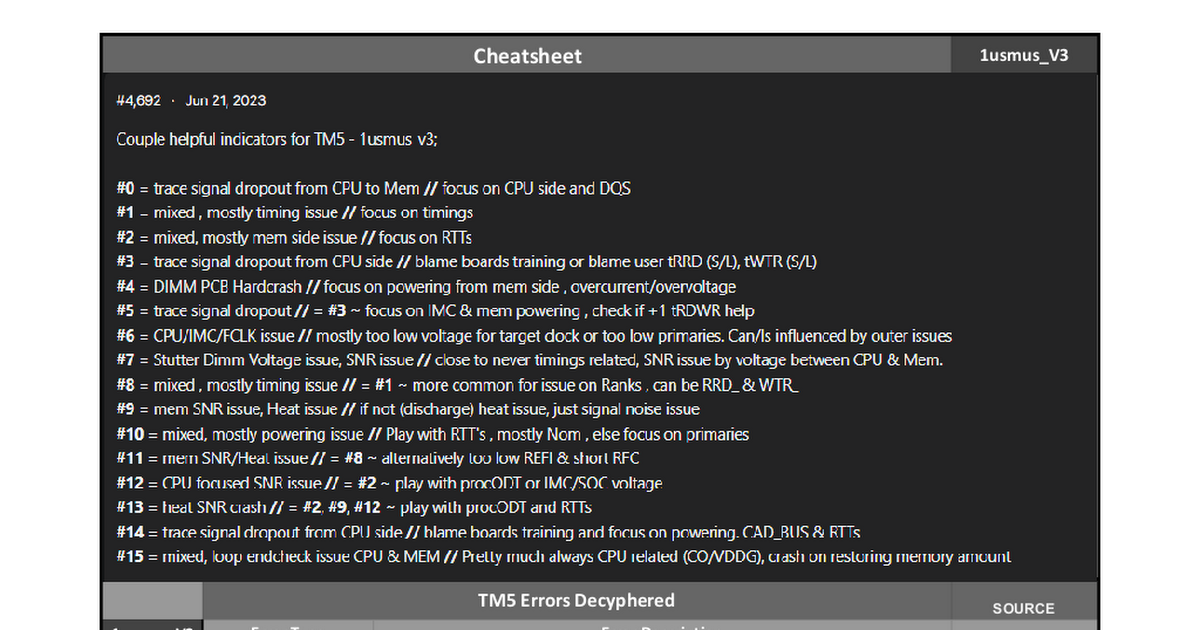

Ensuite, exécutez TM5 1usmus_v3 pendant 25 cycles. Vous devriez être en mesure de trouver facilement vos paramètres stables en utilisant cette méthode dans les quelques heures suivant le réglage des timings avant d'exécuter TM5.

Tout d'abord, chargez un profil de mémoire pour, disons, 6200 à partir de votre carte mère. Réglez la vitesse de la RAM sur 6400.

Ensuite, définissez vos paramètres BUS sur ceux recommandés par @Veii.

Voici les tensions que j'utilise pour 6400 MHz.

Ensuite, définissez vos timings assez élevés, comme ci-dessous, les colonnes de droite. Puis redémarrez.

Hynix DDR5 ne se soucie pas vraiment des tRFC très bas. Définissez le tRFC mini comme ci-dessous pour commencer, puis augmentez le nombre tRC jusqu'à ce que votre PC démarre, ou diminuez-le jusqu'à ce que votre PC ne démarre pas. Ensuite, lorsque votre PC ne démarre pas, augmentez le nombre tRC d'un.

DDR4/5 Helper by Veii

Une fois que c'est aussi bas que vous pouvez aller, vous êtes bon, bien que vous puissiez avoir besoin de l'augmenter d'un cran de plus que le plus bas qu'il démarrera.

Maintenant, exécutez le test Karhu RAM pendant au moins cinq minutes, au maximum dix minutes. Je constate que si cela ne trouve pas d'erreur dans les 5 minutes, je vais normalement bien.

Maintenant, baissez simplement votre tRCDRD et tRP à 39 ou 38.

Karhu a de nouveau couru. Baissez tRCDRD et tRP d'un cran à la fois jusqu'à ce que Karhu obtienne des erreurs, puis augmentez-le d'un cran et laissez-le fonctionner sans erreurs.

Je constate que faire tRCDRD et tRP en premier est le plus important pour devenir stable.

Ensuite, baissez tCL et tRAS jusqu'à ce que vous obteniez des erreurs dans Karhu. Ensuite, augmentez-les tous les deux d'un cran, de sorte que vous n'obteniez aucune erreur.

Ensuite, faites de même avec tWR.

Ensuite, essayez tRTP à 20, cela devrait aller, sinon, essayez un cran plus haut.

Définissez tFAW sur 16 et augmentez-le d'un cran à la fois jusqu'à ce que vous n'obteniez aucune erreur. Entre 16 et 20 devrait être bon.

Ensuite, définissez les TRRDs TtWTRs sur 3-15 ou 4-16. Testez à nouveau.

Définissez ScLs sur 4-4 ou 4-2. Testez à nouveau.

Définissez TrdrdSc et Sd sur 5-5 et TwrwrSd et Dd sur 7-7. Le reste de ces timings comme vous le voyez ci-dessous dans la colonne de gauche des timings. Testez à nouveau.

De plus, si votre BIOS prend en charge le réglage de l'intervalle de rafraîchissement/tREFI, définissez-le au maximum et testez, si cela réussit, bien, sinon, réduisez-le de, disons, 1024, puis testez à nouveau.

Répétez jusqu'à ce que vous n'obteniez aucune erreur dans Karhu Ram Test et enfin TM5.

Vous pouvez voir le Mo/s en survolant le % de couverture dans Karhu.

Ensuite, exécutez TM5 1usmus_v3 pendant 25 cycles. Vous devriez être en mesure de trouver facilement vos paramètres stables en utilisant cette méthode dans les quelques heures suivant le réglage des timings avant d'exécuter TM5.